Data protection from safeguarded anti-fuse OTP memory

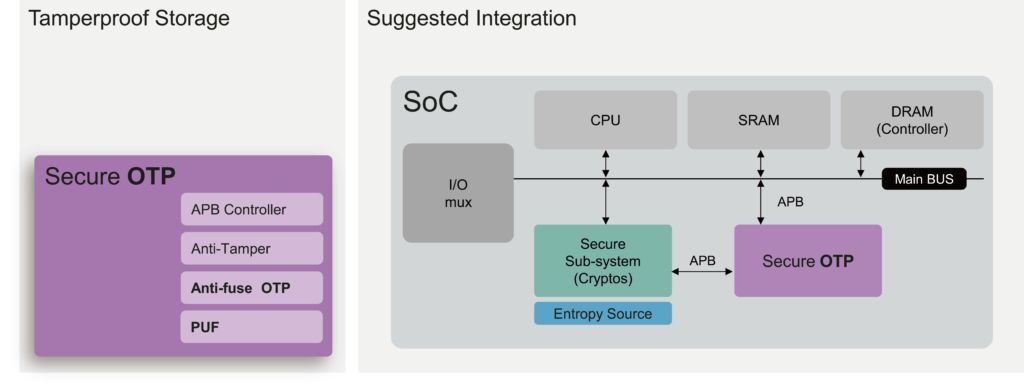

Secure OTP is a combined Physical Macro, and Digital RTL providing comprehensive data protection. It is the ultimate solution for embedded Non-Volatile Memory in CMOS logic or logic-derived technologies. The RTL part provides glue logic of the OTP/PUF controller, tamperproof features, and standard AMBA interfacing. Secure OTPs tailored design maximizes efficiency and allows simplified integration across multiple emerging IC markets and ASIC applications. It is available in various densities and configurations with several CMOS technologies, delivering an embedded non-volatile memory with outstanding reliability and performance.

Secure OTP includes a 1024-bit Physical Unclonable Function (PUF), which is used for physical address scrambling and IO shuffling to enhance stored data security. It is a pure hardware PUF with a virtually ideal entropy that doesn’t require any helper data for error correction, allowing access within a few microseconds.

Secure OTP leads the field in terms of enhanced security OTP platform availability. Through PUFsecurity’s parent company, eMemory, we draw from over 20 years of experience partnering with foundries and delivering high-quality IPs.

Today, the rising security risks to IoT devices are limiting the market’s potential. The answer is creating a collaborative security ecosystem that draws from the safest Hardware, Software, and Operating System solutions. Secure OTP can become the bedrock of any chip security ecosystem and protect critical data such as the root key and the boot code.

Application

Secure OTP safely stores sensitive data such as keys and boot code. In addition, its universal integration and wide availability make it suitable for use across multiple ASIC and SoC applications in, for example, SSD controllers, DPUs, WiFi, PCIe, STB, and Smart TVs.

Features

- Up to 128kb mass production OTP with built-in instant hardware encryption (customization available)

- Comprehensive anti-tamper designs in physical and RTL

- APB control interface with secure/non-secure access privilege

- Four 256-bit hardware PUF fingerprints for scrambling drop-in-use Secure OTP Storage

- Comprehensive permission, zeroization, and lock mechanism to enhance product lifecycle management and protection

- Software stack of Firmware and API

Additional Features

- Autoload: Automatically send trim parameters from OTP upon power-up.

- Secure Boot: Ensure the device only boots up with the authenticated software.