在晶片內安全範圍執行的硬體根密鑰生成和存儲

通過熵碼科技的量子穿隧技術專利,PUFrt硬件信任根為系統安全提供了堅實的基礎,以確保半導體供應鏈的安全,打擊反向工程,並徹底改革了設備認證方式。

層出不窮的資安風險限制了物聯網的潛力。平均而言,一個物聯網設備入網不到5分鐘就會受到第一次攻擊。創建一個環環相扣的安全生態系統是解決這個問題的根本之道,從最安全的硬體、軟體和操作系統解決方案中結合各自的優勢。PUFrt以物理不可複製功能(PUF)的天生晶片指紋為基礎的加密和認證技術核心從最底層的硬體層面保護和串連整個生態系統的安全運作。

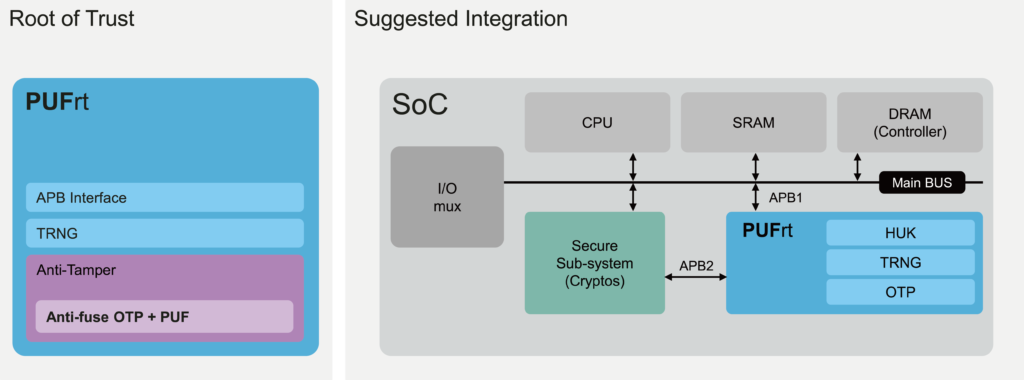

結合了安全的類比設計和數位RTL設計的PUFrt硬件信任根,為市場帶來展新的半導體安全視野。PUFrt內含源自PUF的1024位識別碼、零接觸的密鑰生成、高質量熵源、安全OTP和防篡改設計,集成為一個功能全面的硬體信任根IP。PUFrt可支持各種不同的設計架構,從最基礎的硬體安全密鑰供應,到支持全功能的加密協處理器執行各種安全功能操作,一應俱全。

量產能力是我們是另一市場優勢。母公司力旺電子在市場上20年深耕所留下的經驗與資源,使熵碼的客戶能透過全世界20多個代工廠、高達200多個製程平台取得我們的IP產品進行量產。

產品應用

PUFrt硬件信任根IP為所有芯片設計建立信任基礎,提供實現所有安全操作(如安全啓動)、所須的功能。我們另提供加密引擎的客制化服務,以滿足客戶最切實的需求。

PUFrt具體的應用包括:

- 以安全OTP存儲並保護密鑰和啓動代碼等機敏數據

- 可對多晶片同時進行密鑰配置以降低成本

- 提供加密引擎和安全功能操作的高質量隨機數

產品特點

- 具有安全/非安全訪問權限的APB控制接口

- 四組256-bit具有自我檢測功能的PUF硬件指紋,可作為唯一的私鑰、UID或信任根密鑰使用

- 高質量的真隨機數⽣成器

- 標配8k-bit OTP搭配即時硬體加密。(存儲空間大小可訂製)

- 物理佈局搭配RTL的全面防篡改設計

附加功能

- 自動加載:上電時自動從 OTP 發送調整參數。

- 安全啟動:確保設備僅使用經過驗證的軟體啟動。

- 安全調試:透過調試存取連接埠 (DAP) 抵禦後門攻擊